|

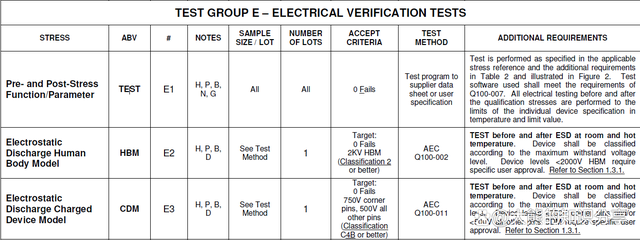

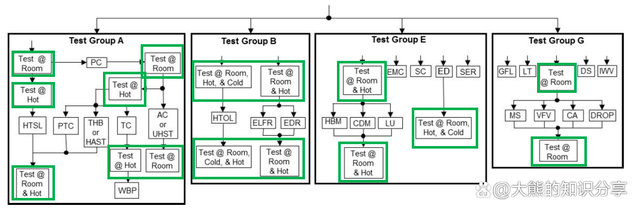

AEC-Q100文件,是芯片开展车规等级验证的重要标准和指导文件。 E组验证是ELECTRICAL VERIFICATION TESTS电气特性验证测试 本文将重点对E组的第1项TEST ---- Pre- and Post-Stress Function/Parameter 应力验证前/后的功能测/性能参数测试项目进行展开讨论。  AEC Q100表2中 E组验证前三项认证内容及说明 很多朋友可能对于TEST的认证内容很是陌生,很少听到有这项验证内容,但是实际上这个内容是验证产品可靠性最重要的一步,它遍布于整个AEC Q100测试流程的下半部分,可以看到下图中,绿色框圈起来的地方多达16项,而且这里面有些项目还要进行高、低、室温测试。  这个测试到底是干什么的呢,实际上就是基于大批量生产线的ATE测试系统,对于进行AEC Q100认证的样品,再次进行测试,所以很多时候我们管这个测试内容叫做回测。

|